# Densitron

**Novel Engineering Worldwide Solutions**

# HD61830 / HD61830B LCD Graphics Controller Chip.

# **Application Notes**

- 1. Introduction

- 2. Main Functions and Features

- 3. Electrical Specifications

- 1. Absolute Maximum Ratings

- 2. Electrical Characteristics

- 4. Interface Pin Connections

- 1. MPU Interface Pin Functions

- 2. LCD Interface Pin Functions

- 5. Timing Characteristics

- 1. MPU Interface Timing

- 2. LCD Interface Timing HD61830

- 3. LCD Interface Timing HD61830B

- 6. System Block Diagram

- 7. Power Supply Sequencing and (Not RST) Terminal

- 8. HD61830(B) Instruction Set

- 1. Mode Control Register

- 2. Character Pitch Register

- 3. Horizontal Count Register

- 4. Multiplex Ratio Register (1/Duty)

- 5. Cursor Position Register

- 6. Display Start Address Registers

- 7. Cursor Address Register (VRAM write address register)

- 8. Write Data to VRAM Instruction

- 9. Read data from VRAM Instruction

- 10. Bit Clear and Bit Set Instructions

- 11. Read BUSY FLAG

- 12. Busy Signal Timing

- 9. Definitions for H<sub>P</sub>, H<sub>N</sub>, V<sub>P</sub>, C<sub>P</sub>, N<sub>X</sub>

- 10. Relationship between Display Mode, VRAM data and LCD dots

- 11. External CG-ROM Pattern

- 12. <u>Recommended Register values for Initializing Densitron Displays</u>

- 1. Character Mode Initialization

- 2. Graphics Mode Initialization

- 3. Initialization Flow Diagram

- 13. Trouble shooting Guide

14. Internal Character Generator Font Pattern and Character Codes 1. Amendment 001 to document AN-01

# 1. INTRODUCTION

The HD61830(B) graphics controller chip is designed to control small to medium size graphic Liquid Crystal Display modules (LCD). It may be interfaced with a number of different 8-bit micro-processor units (MPU). It provides the necessary interface between the MPU and the video RAM (VRAM), sometimes referred to as Display RAM or Refresh RAM. It also generates the necessary timing and data signals for the liquid crystal driver circuits. It has a built-in 192 character Character-Generator ROM (CG-ROM) and Character Generator (CG) circuits. The HD61830(B) has the capability to control upto 64K bytes of external display RAM in graphics mode and 4K bytes in the character mode. Most designs using the HD61830(B) only implement 2K to 8K of VRAM depending on the size of LCD screen. This VRAM may be allocated for text or graphics. The HD61830(B) can support a wide variety of LCD formats.

This application note is not written with any specific display in mind but is intended to give a thorough understanding of how to use the HD61830(B) and implement the software/hardware interface. Some LCD modules will have the HD61830(B) controller built into the module such as the LM31XX and LM41XX series of LCD modules, others require an external graphics controller. This application note is applicable to the LM1001GC, LM1002GC and LM1006GC graphics controller cards available from Densitron as well as to Densitron LCD modules with on-board HD61830(B) graphics controllers.

# 2. Main Functions and Features of the HD61830

- Simple 8-bit parallel Interface

- Built in Character Generator and font table (160, 5x7 plus 32, 5x11 characters)

- External CG-ROM option for upto 256 character font table

- Software Selectable Cursor ON/OFF/BLINK attributes

- Software instructions for scrolling, character blink and bit manipulation

- Software Selectable Character or Graphics modes

- Software selectable Duty (1 to 1/128)

- Software Selectable Character Cell size (6x8 upto 8x16)

- Low power CMOS design

**Note:**Not all these features are implemented on Densitron LCD modules or LM100X series controller cards.

# 3. Electrical Specifications for HD61830/HD61830B

#### 3.1 Absolute Maximum Ratings

| Item                  | Symbol           | Value                        | Units |

|-----------------------|------------------|------------------------------|-------|

| Power supply voltage  | V <sub>CC</sub>  | -0.3 to 7.0                  | V     |

| Input voltage         | V <sub>in</sub>  | -0.3 to V <sub>CC</sub> +0.3 | V     |

| Operating Temperature | T <sub>op</sub>  | -20 to 75                    | °C    |

| Storage Temperature   | T <sub>stg</sub> | -55 to 125                   | °C    |

| Note:                 |                  |                              |       |

- 1. All voltages are referenced to GND=0V

- 2. Specification is for HD61830(B) only. LCD module specifications may differ.

# **3.2 Electrical Characteristics**

| ltem                    |      | Symbol                              | Condition                                                                    | Min                  | Max             | Units | Notes   |

|-------------------------|------|-------------------------------------|------------------------------------------------------------------------------|----------------------|-----------------|-------|---------|

| Input voltage           | "H"  | V <sub>IH</sub>                     |                                                                              | 2.2                  | V <sub>CC</sub> | V     | 1, 4    |

| (TTL Level)             | "L"  | V <sub>IL</sub>                     |                                                                              | 0                    | 0.8             | V     | 1, 2, 4 |

|                         | "H"  | V <sub>IHR</sub>                    |                                                                              | 3.0                  | V <sub>CC</sub> | V     | 2       |

| Input voltage           |      | V <sub>IHC</sub>                    |                                                                              | $0.7V_{CC}$          | V <sub>CC</sub> | V     | 3, 7    |

| (CMOS Level)            | "L"  | V <sub>ILC</sub>                    |                                                                              | 0                    | $0.3V_{CC}$     | V     | 3, 7    |

| Output voltage          | "H"  | V <sub>OH</sub>                     | -I <sub>OH</sub> =0.6mA                                                      | 2.4                  | V <sub>CC</sub> | V     | 4       |

| (TTL level)             | "L"  | V <sub>OL</sub>                     | I <sub>OL</sub> =1.6mA                                                       | 0                    | 0.4             | V     | 4       |

| Output voltage          | "H"  | V <sub>OHC</sub>                    | -I <sub>OH</sub> =0.6mA                                                      | V <sub>CC</sub> -0.4 | V <sub>CC</sub> | V     | 5, 6    |

| (CMOS level)            | "L"  | V <sub>OLC</sub>                    | I <sub>OL</sub> =0.6mA                                                       | 0                    | 0.4             | V     | 5, 6    |

| Input leakage currer    | nt   | I <sub>IL</sub>                     | V <sub>in</sub> =0~V <sub>CC</sub>                                           | -5                   | 5               | μA    | 4       |

| Output leakage curr     | ent  | I <sub>OL</sub>                     | V <sub>out</sub> =0~V <sub>CC</sub>                                          | -10                  | 10              | μA    | 4       |

| Internal Oscillation    |      | f <sub>osc</sub>                    | C <sub>f</sub> =15p±5%<br>R <sub>f</sub> =39K±2%<br>f <sub>osc</sub> =500KHz |                      | 600             | KHz   | 3       |

| External clock frequ    | ency | f <sub>cp</sub>                     |                                                                              | 100<br>100           | 1100<br>2400    | KHz   | 37      |

| External clock Duty     |      | Duty                                |                                                                              | 47.5                 | 52.5            | %     | 3, 7    |

| Ext. clock rise/fall ti | me   | t <sub>rcp</sub> , t <sub>fcp</sub> |                                                                              | -                    | 50<br>25        | ns    | 3<br>7  |

(V<sub>CC</sub>=+5V±10%, GND=0V, Ta=-20 to +75°C)

#### Notes:

- 1. E, (Not CS), RS, R/(Not W)

- 2. (Not RST)

3. CR for HD61830

4. DB0 to DB7

- FLM, CL1, CL2

D1, D2, M

- 7. CR for HD61830B

# 4. Interface Pin Connections

#### **4.1 MPU Interface Pin Functions**

Pin-outs differ for individual LCD modules with on-board controllers. Please refer to individual module data sheets for pin assignment information.

| Pin Name        | I/O | Pin Function                                                        |  |  |  |  |  |  |  |

|-----------------|-----|---------------------------------------------------------------------|--|--|--|--|--|--|--|

| V <sub>SS</sub> | -   | Ground                                                              |  |  |  |  |  |  |  |

| V <sub>CC</sub> | -   | _ogic Supply (+5V)                                                  |  |  |  |  |  |  |  |

| RS              | I   | Register Select: "1" = Instruction Register<br>"0" = Data Register  |  |  |  |  |  |  |  |

| R/(Not W)       | I   | Read/Write: "1" = Read from HD61830(B)<br>"0" = Write to HD61830(B) |  |  |  |  |  |  |  |

| E               | I   | Enable (Active High)                                                |  |  |  |  |  |  |  |

| DB0             | I/O | Bi-directional Data Bus Line 0                                      |  |  |  |  |  |  |  |

| DR1             | I/O | Ri-directional Data Rus Line 1                                      |  |  |  |  |  |  |  |

|           | " U |                                |

|-----------|-----|--------------------------------|

| DB2       | I/O | Bi-directional Data Bus Line 2 |

| DB3       | I/O | Bi-directional Data Bus Line 3 |

| DB4       | I/O | Bi-directional Data Bus Line 4 |

| DB5       | I/O | Bi-directional Data Bus Line 5 |

| DB6       | I/O | Bi-directional Data Bus Line 6 |

| DB7       | I/O | Bi-directional Data Bus Line 7 |

| (Not CS)  | I   | Chip Select (Active Low)       |

| (Not RST) | Ι   | Reset (Active Low)             |

# 4.2 LCD Interface Pin Functions

For LCD modules with on-board controllers, these signals are not generally accessible. However for the LM1001GC, LM1002GC and LM1006GC graphics controller cards these signals are available; refer to individual data sheets for pin assignments.

| I/O | Pin Function                                                                              |  |  |  |  |  |  |  |  |  |

|-----|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 0   | Serial Data Line 1                                                                        |  |  |  |  |  |  |  |  |  |

| 0   | First Line Marker (Start of Frame)                                                        |  |  |  |  |  |  |  |  |  |

| 0   | Control Signal for AC drive of LC                                                         |  |  |  |  |  |  |  |  |  |

| 0   | atch clock                                                                                |  |  |  |  |  |  |  |  |  |

| 0   | Shift clock for serial data                                                               |  |  |  |  |  |  |  |  |  |

| 0   | Serial Data Line 2                                                                        |  |  |  |  |  |  |  |  |  |

| -   | Power supply for logic circuits                                                           |  |  |  |  |  |  |  |  |  |

| -   | Ground                                                                                    |  |  |  |  |  |  |  |  |  |

| -   | Power supply for LC drivers                                                               |  |  |  |  |  |  |  |  |  |

| -   | Operating voltage for LC drivers (Contrast)                                               |  |  |  |  |  |  |  |  |  |

|     | <ul> <li>I/O</li> <li>O</li> <li>O</li> <li>O</li> <li>O</li> <li>-</li> <li>-</li> </ul> |  |  |  |  |  |  |  |  |  |

# 5. Timing Characteristics

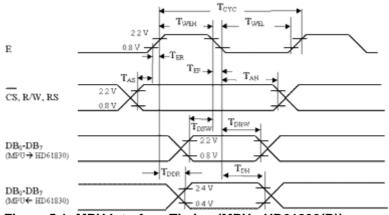

## 5.1 MPU Interface Timing (MPU - HD61830)

| Item                |      | Symbol            | Min  | Тур | Max | Unit |

|---------------------|------|-------------------|------|-----|-----|------|

| Enable cycle time   |      | t <sub>CYC</sub>  | 1.0  | -   | -   | μs   |

| Enable pulse width  | "H"  | t <sub>WEH</sub>  | 0.45 | -   | -   | μs   |

|                     | "L"  | t <sub>WEL</sub>  | 0.45 | -   | -   | μs   |

| Enable rise time    |      | t <sub>Er</sub>   | -    | -   | 25  | ns   |

| Enable fall time    |      | t <sub>Ef</sub>   | -    | -   | 25  | ns   |

| Set up time         |      | t <sub>AS</sub>   | 140  | -   | -   | ns   |

| Data set up time    |      | t <sub>DSW</sub>  | 225  | -   | -   | ns   |

| Data delay time     |      | t <sub>DDR</sub>  | -    | -   | 225 | ns   |

| Data hold time (Wri | te)  | t <sub>DHW</sub>  | 10   | -   | -   | ns   |

| Address hold time   |      | t <sub>AH</sub>   | 10   | -   | -   | ns   |

| Data Hold Time (Re  | ead) | tDH               | 20   | -   | -   | ns   |

| Pulse width of /RES | 3    | t <sub>WRES</sub> | 1µs  | -   | 2ms | -    |

Note: MPU interface timing for HD61830B is identical to HD61830

Figure 5.1: MPU Interface Timing (MPU - HD61830(B))

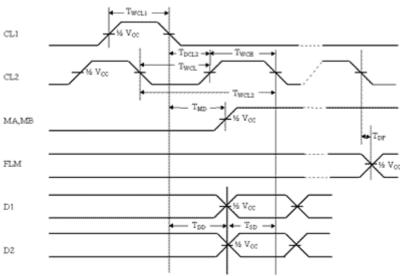

## 5.2 LCD Interface Timing (HD61830 - LCD)

| ltem                      |                                | Symbol            | Min | Тур | Max | Unit |  |  |

|---------------------------|--------------------------------|-------------------|-----|-----|-----|------|--|--|

| Clock pulse width (high l | Clock pulse width (high level) |                   |     |     |     |      |  |  |

| Clock delay time          |                                | t <sub>DCL2</sub> | -   | -   | 200 | ns   |  |  |

| Clock cycle time          |                                | t <sub>WCL2</sub> | 900 | -   | -   | ns   |  |  |

| Clock pulse width         | "H"                            | t <sub>WCH</sub>  | 450 | -   | -   | ns   |  |  |

|                           | "L"                            | t <sub>WCL</sub>  | 450 | -   | -   | ns   |  |  |

| M delay time              |                                | t <sub>MD</sub>   | -   | -   | 300 | ns   |  |  |

| FLM delay time            |                                | t <sub>DF</sub>   | -   | -   | 300 | ns   |  |  |

| Data delay time           | t <sub>DD</sub>                | -                 | -   | 200 | ns  |      |  |  |

| Data set up time          |                                | t <sub>SD</sub>   | 250 | -   | -   | ns   |  |  |

Note: No load is applied to all outputs.

Figure 5.2: LCD Interface Timing (HD61830 - LCD)

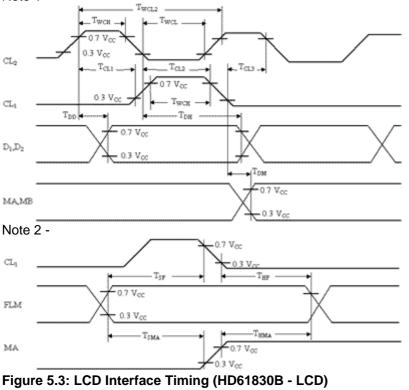

# 5.3 LCD Interface Timing (HD61830B - LCD)

| Item              |                  | Symbol           | Min  | Тур | Max | Unit | Note |

|-------------------|------------------|------------------|------|-----|-----|------|------|

| Clock cycle tim   | Clock cycle time |                  |      |     | -   | ns   | 1    |

| Clock pulse width | "H"              | t <sub>WCH</sub> | 150  | -   | -   | ns   | 1    |

|                   | "L"              | t <sub>WCL</sub> | 150  | -   | -   | ns   | 1    |

| Data delay time   |                  | t <sub>DD</sub>  | -    | -   | 50  | ns   | 1    |

| Data hold time    |                  | t <sub>DH</sub>  | 100  | -   | -   | ns   | 1    |

| M delay time      |                  | t <sub>DM</sub>  | -200 | -   | 200 | ns   | 1    |

| FLM set up time   |                  | t <sub>SF</sub>  | 400  | -   | -   | ns   | 2    |

| FLM hold time     |                  | t <sub>HF</sub>  | 1000 | -   | -   | ns   | 2    |

| M set up time     |                  | t <sub>SMA</sub> | 400  | -   | -   | ns   | 2    |

| M hold time       |                  | t <sub>HMA</sub> | 1000 | -   | -   | ns   | 2    |

Note 1 -

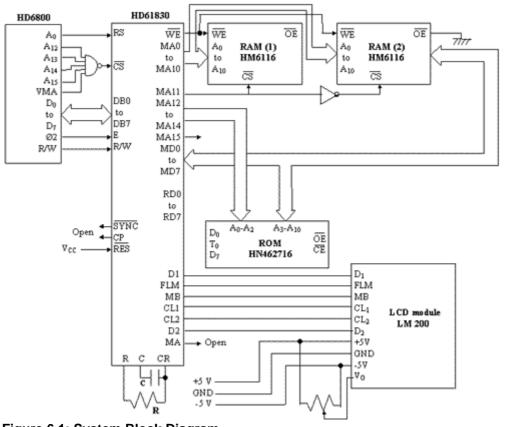

# 6. System Block Diagram

All liquid crystal displays require two power sources  $V_{CC}$  for logic circuits and  $V_{EE}$  for Liquid Crystal (LC) drive. Some graphics LCD modules will run directly of a single  $V_{CC}$  supply by generating the  $V_{EE}$  voltage on-board; others will require an external DC-DC converter to generate the negative  $V_{EE}$  voltage. Refer to individual specifications for details.

Figure 6.1: System Block Diagram

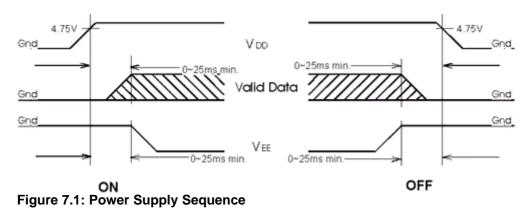

# 7. Power Supply Sequencing and (Not RST) Terminal

To prevent latch-up of the CMOS LSI (HD61830(B) and LCD driver LSI) ensure your systems power supply follows the following sequence. The  $V_{DD}$  must be applied with a small time delay befor  $V_{EE}$  is turned on. It is very important to follow this sequence in order to prevent the CMOS LSI from latching up and to prevent DC signals from being applied to the LC material. If the  $V_{EE}$  voltage is applied before the timing signals M, CL1, CL2, and FLM then a DC voltage will be applied to the LC material. Over time this will degrade the LC fluid performance due to their electro-chemical behavior. If this power-up sequence is not adhered to, permanent damage to the LCD module may result.

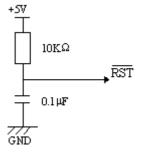

The RESET circuit shown in Figure 7.2 is recommended to correctly reset the HD61830(B). On RESET the internal registers of the HD61830(B) are cleared and the BUSY flag is reset, Display is turned off,  $H_p$ =6 and HD61830 is set for Slave mode (Refer to section 8 for detail).

Figure 7.2: RESET Circuit

# 8. HD61830(B) Instruction Set

The following is a summary of available instructions for use with the HD61830(B).

| R/Not W |   |                     | DB6                |                   |       | DB3                | DB2                | DB1                            | DB0<br>LSB | Function                        |

|---------|---|---------------------|--------------------|-------------------|-------|--------------------|--------------------|--------------------------------|------------|---------------------------------|

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 0                  | 0                  | 0                              | 0          | Set Mode Control Register       |

| 0       | 0 | 0                   | 0                  | Mode              | e Con | trol da            | ata                |                                |            | Mode Control data               |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 0                  | 0                  | 0                              | 1          | Set Character Pitch Register    |

| 0       | 0 | (V <sub>P</sub> -1) | ) bina             | ry                |       | 0                  | (H <sub>P</sub> -1 | l) bina                        | ary        | Vert./Horiz. Pitch data         |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 0                  | 0                  | 1                              | 0          | Set Horizontal Count Register   |

| 0       | 0 | 0                   | (H <sub>N</sub> -1 | l) bina           | ary   |                    |                    |                                |            | Horizontal Count data           |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 0                  | 0                  | 1                              | 1          | Set Multiplex Ratio Register    |

| 0       | 0 | 0                   | (N <sub>X</sub> -1 | l) bina           | ary   |                    |                    |                                |            | Multiplex ratio data (1/Duty-1) |

|         | 1 | 0                   | 0                  | 0                 | 0     | 0                  | 1                  | 0                              | 0          | Set Cursor Position Register    |

| 0       | 0 | 0                   | 0                  | 0                 | 0     | (C <sub>P</sub> -1 | ) bina             | ary                            |            | Cursor Position data            |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 1                  | 0                  | 0                              | 0          | Set Lower Dis. Start Addr Reg   |

| 0       | 0 | (Low                | order              | Displ             | ay St | art Ac             | ary                | Lower Display Start Addr. data |            |                                 |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 1                  | 0                  | 0                              | 1          | Set Upper Dis. Start Addr Reg   |

| 0       | 0 | (High               | order              | r Disp            | lay S | tart A             | ddres              | s) bin                         | ary        | Upper Display Start Addr. data  |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 1                  | 0                  | 1                              | 0          | Set Lower Cursor Addr Reg       |

| 0       | 0 | (Low                | order              | Curs              | or Ad | dress              | ) bina             | ry                             |            | Lower Cursor Address data       |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 1                  | 0                  | 1                              | 1          | Set Upper Cursor Addr Reg       |

| 0       | 0 | (High               | order              | <sup>-</sup> Curs | or Ad | Idress             | s) bina            | ary                            |            | Upper Cursor Address data       |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 1                  | 1                  | 0                              | 0          | Write-VRAM Instruction          |

| 0       | 0 | MSB                 | (Char              | acter             | code  | or bit             | -map               | data                           | ) LSB      | Display data                    |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 1                  | 1                  | 0                              | 1          | Read-VRAM Instruction           |

| 1       | 0 | MSB                 | (Char              | acter             | code  | or bit             | -map               | data                           | ) LSB      | Display data                    |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 1                  | 1                  | 1                              | 0          | Bit Clear Instruction           |

| 0       | 0 | 0                   | 0                  | 0                 | 0     | 0                  | (N <sub>B</sub> -1 | l) bina                        | ary        | Bit Address                     |

| 0       | 1 | 0                   | 0                  | 0                 | 0     | 1                  | 1                  | 1                              | 1          | Bit Set Instruction             |

| 0       | 0 | 0                   | 0                  | 0                 | 0     | 0                  | (N <sub>B</sub> -1 | ) bina                         | ary        | Bit Address                     |

| 1       | 1 | BF                  | *                  | *                 | *     | *                  | *                  | *                              | *          | Read BUSY FLAG                  |

|         |   |                     |                    |                   |       |                    |                    |                                |            |                                 |

Table 8.0: HD61830(B) Instruction Set

#### Note:

1. \* = DON'T CARE

2. Read the status of the Busy Flag before each new instruction is sent to the HD61830(B). If the

HD61830(B) Busy Flag is set (BF=1) then the HD61830(B) is busy processing the previous instruction. If a new instruction is sent to the HD61830(B) while the Busy Flag, BF=1, then that command shall be ignored by the HD61830(B).

- 3. Vertical Character Pitch,  $V_P: 0 \le (V_P-1) \le 15$

- 4. Horizontal Character Pitch,  $H_P: 5 \le (H_P-1) \le 7$

- 5. Horizontal Character Count,  $H_N:H_N \leq 128$ ,  $H_N$  must be an even integer.

- 6. Multiplex Ratio,  $N_X$ :  $N_X = 1/Duty$ ,  $N_X \le 128$

#### 8.1 Mode Control Register

| R/Not W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Function                   |

|---------|----|-----|-----|-----|-----|-----|-----|-----|-----|----------------------------|

| 0       | 1  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Set Mode Control Register  |

| 0       | 0  | 0   | 0   | D5  | D4  | D3  | D2  | D1  | D0  | Mode Control data          |

|         |    |     |     |     |     |     |     |     | 0   | HD61830(B) Internal CG ROM |

|         |    |     |     |     |     |     |     |     | 1   | External CG ROM            |

|         |    |     |     |     |     |     |     | 0   |     | Character mode             |

|         |    |     |     |     |     |     |     | 1   |     | Graphics mode              |

|         |    |     |     |     |     | 0   | 0   |     |     | Cursor OFF                 |

|         |    |     |     |     |     | 0   | 1   |     |     | Cursor ON                  |

|         |    |     |     |     |     | 1   | 0   |     |     | Cursor OFF Character Blink |

|         |    |     |     |     |     | 1   | 1   |     |     | Cursor blank               |

|         |    |     |     |     | 0   |     |     |     |     | Slave Mode                 |

|         |    |     |     |     | 1   |     |     |     |     | Master Mode                |

|         |    |     |     | 0   |     |     |     |     |     | Display OFF                |

|         |    |     |     | 1   |     |     |     |     |     | Display ON                 |

The Mode Control register sets the operating mode for the HD61830(B). It controls the character/graphics mode, cursor, on/off/blink, master/slave and display on/off. When D1 is set to 1 and D0, D2 and D3 are set to 0, the HD61830(B) is set to graphics mode and the character generator and cursor functions are disabled.

Most displays and controller cards use only one HD61830 so D4=1. The LM1006GC is the exception as two HD61830 are used; one configured as the slave (D4=0) and the other as the master (D4=1).

#### 8.2 Character Pitch Register

| R/Not W | RS | DB7                | DB6    | DB5 | DB4 | DB3 | DB2                        | DB1 | DB0 | Function                     |

|---------|----|--------------------|--------|-----|-----|-----|----------------------------|-----|-----|------------------------------|

| 0       | 1  | 0                  | 0      | 0   | 0   | 0   | 0                          | 0   | 0   | Set Character Pitch Register |

| 0       | 0  | (V <sub>P</sub> -′ | 1) bin | ary |     | 0   | (H <sub>P</sub> -1) binary |     |     | Vert./Horiz. Pitch data      |

**Character Mode:**  $V_P$  and  $H_P$  set the horizontal and vertical size of each character cell. To display the 5x11 font stored in the CG-ROM set  $V_P$ =12 and  $H_P$ =6. That is set the Character Pitch register to B5H. If displaying only the 5x7 font then set VP=8 and HP=6. That is set the Character Pitch register to 75H. A value in the range of 1 to 16 may be used for  $V_P$ . A value in the range of 6 to 8 may be used for  $H_P$ . Refer to section 9.0 for pictorial definitions of  $V_P$  and  $H_P$ .

<u>**Graphics Mode:**</u> $V_P$  has no meaning in Graphics mode and may be set to any value.  $H_P$  should be set to 8. That is set Character Pitch register to 07H for Graphics mode.

## 8.3 Horizontal Count Register

| R/Not W | RS | DB7 | DB6                | DB5    | DB4 | DB3 | DB2 | DB1 | DB0 | Function                         |

|---------|----|-----|--------------------|--------|-----|-----|-----|-----|-----|----------------------------------|

| 0       | 1  | 0   | 0                  | 0      | 0   | 0   | 0   | 1   | 0   | Set Horizontal Count Instruction |

| 0       | 0  | 0   | (H <sub>N</sub> -′ | 1) bin | ary |     |     |     |     | Horizontal Count data            |

<u>Character Mode</u>: This register sets the number of horizontal characters that can be displayed on the LCD. The character width is defined by  $H_P$  in the Character Pitch Register (Section 8.2).

<u>Graphics Mode</u>: This register sets the number of horizontal bytes that can be displayed on the LCD. For graphics mode, it is best to set  $H_p=8$ .

If the total number of horizontal dots on the LCD screen is **n** then:

#### $H_N = n / H_P$

**Note:** HN must be an <u>even integer value</u> in the range  $2 \le HN \le 128$

**For example:** If using HD61830(B) to control a 64x240 LCD screen in Character Mode, with HP=6 then set HN=28H. That is, write 27H into Horizontal Count register.

#### 8.4 Multiplex Ratio Register (1/Duty)

| R/Not W | RS | DB7 | DB6  | DB5    | DB4  | DB3 | DB2 | DB1 | DB0 | Function                          |

|---------|----|-----|------|--------|------|-----|-----|-----|-----|-----------------------------------|

| 0       | 1  | 0   | 0    | 0      | 0    | 0   | 0   | 1   | 1   | Set Multiplex Ratio Register      |

| 0       | 0  | 0   | (NX- | 1) bir | nary |     |     |     |     | Multiplex ratio data [(1/Duty)-1] |

Set N<sub>x</sub> to the Duty cycle ratio of the LCD being used. N<sub>x</sub> should be in the range  $1 \le N_x \le 128$ .

For example: for a 1/64 duty LCD screen set  $N_x$ =64 and write 3FH into Multiplex Ratio register.

#### 8.5 Cursor Position Register

| R/Not W | RS | DB7 | DB6 | DB5 | DB4 | DB3                        | DB2 | DB1 | DB0 | Function                     |

|---------|----|-----|-----|-----|-----|----------------------------|-----|-----|-----|------------------------------|

| 0       | 1  | 0   | 0   | 0   | 0   | 0                          | 1   | 0   | 0   | Set Cursor Position Register |

| 0       | 0  | 0   | 0   | 0   | 0   | (C <sub>P</sub> -1) binary |     |     |     | Cursor Position data         |

In Character Mode,  $C_P$  indicates the position of the cursor within the character cell defined by  $V_P$  and  $H_P$  in the Character Pitch register (Section 8.2). The horizontal width of the cursor is equal to  $H_P$ . A value of 1 to 16 may be set for  $C_P$ . If  $C_P > V_P$  no cursor will be displayed. If  $C_P \le V_P$  the cursor has higher priority and the cursor shall be written over the top of the character on the LCD screen.  $C_P=1$  means cursor will appear on top row of character cell; if  $C_P=V_P$  then cursor will appear on bottom row of character cell.

**For example:**To display a cursor underneath a 5x7 character, set  $C_p$ =8. That is write 07H into Cursor Position register. To display a cursor underneath a 5x11 character, set  $C_p$ =12. That is write 0BH into Cursor Position register.

#### 8.6 Display Start Address Registers

| R/Not W | RS | DB7                                                                      | DB6                                     | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Function                      |  |  |  |

|---------|----|--------------------------------------------------------------------------|-----------------------------------------|-----|-----|-----|-----|-----|-----|-------------------------------|--|--|--|

| 0       | 1  | 0                                                                        | 0                                       | 0   | 0   | 1   | 0   | 0   | 0   | Set Lower Dis. Start Addr Reg |  |  |  |

| 0       | 0  | (Low order Display Start Address) binary Lower Display start Addr. data  |                                         |     |     |     |     |     |     |                               |  |  |  |

| 0       | 1  | 0                                                                        | 0 0 1 0 1 Set Upper Dis. Start Addr Reg |     |     |     |     |     |     |                               |  |  |  |

| 0       | 0  | (High order Display Start Address) binary Upper Display Start Addr. data |                                         |     |     |     |     |     |     |                               |  |  |  |

The High and Low order Display Start Address indicates a VRAM address at which the data displayed at the top left corner of the LCD screen is stored.

<u>Character Mode</u>:Set DB7~DB4 = 0, for High order Display Start Address. Only DB3~DB0 is valid for High order Display Start Address in the Character Mode. That is a value in the range of 0000H to 0FFFH may be written into the High/Low order Display Start Address registers for the HD61830(B) Character Mode.

<u>Graphics Mode</u>: All 16 bits of the High/Low order Display Start Address register are valid for the Graphics Mode of the HD61830(B). A value in the range 0000H to FFFFH may be written into the High/Low order Display Start Address registers. However bear in mind that not all LCD modules or controller cards have this much addressable RAM on-board. Refer to individual LCD module specifications for size of addressable VRAM.

The Display Start Address registers are very useful when implementing scrolling both horizontally and vertically. The Display Start Address may be incremented or decremented by the value  $H_N$  (section 8.3) to scroll up or down by one row of dots in the Graphics mode or by one character row (set by VP) in the Character mode. By incrementing/decrementing the Display Start Address by one will cause the LCD screen to shift horizontally left/right by the number of dots set by the value  $H_P$  (section 8.2) as shown by below.

#### For Example:

|   | В |   |      |  | D |   |   | A | В | С | <br> |  | D | Ε |   |

|---|---|---|------|--|---|---|---|---|---|---|------|--|---|---|---|

| Ε | F | G |      |  | Η |   |   |   | F | G |      |  | Н | Ι |   |

| I | I |   |      |  | Ι |   |   |   |   |   |      |  |   |   |   |

|   |   |   |      |  |   |   |   |   |   |   |      |  |   |   |   |

|   |   |   |      |  | Ι |   |   |   |   | Ι |      |  |   |   |   |

|   |   |   |      |  |   |   |   |   |   |   |      |  |   |   |   |

|   | Ι |   |      |  | I |   |   |   |   | I |      |  |   |   |   |

|   |   |   |      |  |   |   |   |   |   |   |      |  |   | J |   |

| J | Κ | L | <br> |  | Μ |   |   |   | Κ | L | <br> |  | Μ | Ν |   |

| Ν | 0 | Ρ | <br> |  | Q | R | S |   | Ο | Ρ | <br> |  | Q | R | S |

Before Incrementing Display Start Address.... After Incrementing Display Start Address....

#### 8.7 Cursor Address Register (VRAM write address register)

| R/Not W | RS | DB7   | DB6    | DB5   | DB4    | DB3                       | DB2    | DB1                       | DB0                       | Function                  |

|---------|----|-------|--------|-------|--------|---------------------------|--------|---------------------------|---------------------------|---------------------------|

| 0       | 1  | 0     | 0      | 0     | 0      | 1                         | 0      | 1                         | 0                         | Set Lower Cursor Addr Reg |

| 0       | 0  | (Low  | orde   | r Cur | sor A  | ddre                      | ss) bi |                           | Lower Cursor Address data |                           |

| 0       | 1  | 0     | 0      | 0     | 0      | 1                         | 0      | Set Upper Cursor Addr Reg |                           |                           |

| 0       | 0  | (Higł | n orde | er Cu | rsor A | Upper Cursor Address data |        |                           |                           |                           |

The Cursor Address registers set the address for reading/writing display data to the VRAM. Always write to the Low Order Cursor Address register first followed by the High order Cursor Address register. The High order Cursor Address register may be updated independently from the Low order Cursor Address register; however if the Low order Cursor Address register is updated then the High order Cursor Address register must also be updated directly afterwards.

The Cursor Address is automatically incremented by +1 after each successive Write-VRAM, Read-VRAM, Bit Set or Bit Clear instruction.

**<u>Character Mode</u>**: Set DB7~DB4 = 0, for High order Cursor Address. Only DB3~DB0 is valid for High order Cursor Address in the Character Mode. That is a value in the range of 0000H to 0FFFH may be written into the High/Low order Display Start Address registers for the HD61830(B) Character Mode.

<u>Graphics Mode</u>: All 16 bits of the High/Low order Cursor Address register are valid for the Graphics Mode of the HD61830(B). A value in the range 0000H to FFFFH may be written into the High/Low order Cursor Address registers. However bear in mind that not all LCD modules have this much addressable RAM on-board. Refer to individual LCD module specifications for size of addressable VRAM.

#### 8.8 Write Data to VRAM Instruction

| R/Not W | RS | DB7 | DB6  | DB5    | DB4  | DB3    | DB2  | DB1   | DB0 | Function               |

|---------|----|-----|------|--------|------|--------|------|-------|-----|------------------------|

| 0       | 1  | 0   | 0    | 0      | 0    | 1      | 1    | 0     | 0   | Write-VRAM Instruction |

| 0       | 0  | MSB | (Cha | racter | code | or bit | -map | data) | LSB | Display data           |

**Character Mode:** This instruction will load the character code data into VRAM at the address specified by the current value stored in the Cursor Address register (section 8.7). The Cursor Address register will increment by +1 after each successive Write-VRAM instruction. Therefore to write **DENSITRON** to VRAM address 01FFH, write the following sequence of commands to the HD61830(B):

| STEP #  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 |

|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| DB7~DB0 | 0A | FF | 0B | 01 | 0C | 44 | 45 | 4E | 53 | 49 | 54 | 52 | 4F | 4E |

| RS      | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| R/Not W | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Note: Check Busy Flag (BF) before steps 1, 3, and 5. All values are hexadecimal.

In order to move the word **DENSITRON** so that it is visible at the top left hand corner of the LCD screen set the Display Start Address register to 01FFH (section 8.6). Note that if the character code written to VRAM is not recognized by the CG-ROM then a blank character will be displayed on the LCD screen (Refer to section 14.0).

<u>Graphics Mode</u>: This instruction will load a byte of data into VRAM at the address specified by the current value stored in the Cursor Address (section 8.7). The Cursor Address register will increment by +1 after each successive Write-Vram instruction. The least significant bit (LSB) of each byte written to VRAM correspondes to the left most dot on the LCD screen (See section 10.0)

#### 8.9 Read data from VRAM Instruction

| R/Not W | RS | DB7 | DB6  | DB5    | DB4  | DB3    | DB2   | DB1   | DB0 | Function              |

|---------|----|-----|------|--------|------|--------|-------|-------|-----|-----------------------|

| 0       | 1  | 0   | 0    | 0      | 0    | 1      | 1     | 0     | 1   | Read-VRAM Instruction |

| 1       | 0  | MSB | (Cha | racter | code | or bit | t-map | data) | LSB | Display data          |

This instruction outputs the data stored in the VRAM at the address immediately preceding the current Cursor Address. The Cursor Address is incremented by +1 after each successive Read-VRAM instruction. To read the VRAM data at the current Cursor Address it will be necessary to do a dummy Read-VRAM instruction so that the Cursor address is incremented by +1 before issuing the next read instruction which will put valid data on the data bus. For example assume **DENSITRON** is stored in VRAM starting at address 01FFH. The following sequence will read the data stored at addresses 01FFH to 0208H. Note the dummy read at step number 6. It is important to remember to make one dummy read when reading data after setting the Cursor Address register.

| STEP #  | 1  | 2  | 3  | 4  | 5  | 6 | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|---------|----|----|----|----|----|---|----|----|----|----|----|----|----|----|----|

| DB7~DB0 | 0A | FF | 0B | 01 | 0D | * | 44 | 45 | 4E | 53 | 49 | 54 | 52 | 4F | 4E |

| RS      | 1  | 0  | 1  | 0  | 1  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| R/Not W | 0  | 0  | 0  | 0  | 0  | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Note: Check Busy Flag (BF) before steps 1, 3, and 5. All values are hexadecimal.

#### 8.10 Bit Clear and Bit Set Instructions

| R/Not W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2                        | DB1    | DB0 | Function                     |

|---------|----|-----|-----|-----|-----|-----|----------------------------|--------|-----|------------------------------|

| 0       | 1  | 0   | 0   | 0   | 0   | 1   | 1                          | 1      | 0   | <b>Bit Clear Instruction</b> |

| 0       | 0  | 0   | 0   | 0   | 0   | 0   | (N <sub>B</sub> -′         | 1) bin | ary | Bit Address                  |

| 0       | 1  | 0   | 0   | 0   | 0   | 1   | 1                          | 1      | 1   | Bit Set Instruction          |

| 0       | 0  | 0   | 0   | 0   | 0   | 0   | (N <sub>B</sub> -1) binary |        |     | Bit Address                  |

The Clear/Set Bit instructions reset/set 1 bit in a byte of VRAM data to 0 or 1, respectively. The position of the bit in a byte is defined by NB. NB=1 refers to the LSB, D0. NB=8 refers to the MSB, D7.

The Cursor Address is automatically incremented by +1 after execution of these instructions. For example; to clear bit D4 of address 01FFH and set bits D1 and D6 of 0200H use the following sequence:

| STEP #  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 |

|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| DB7~DB0 | 0A | FF | 0B | 01 | 0E | 04 | 0F | 01 | 0A | 00 | 0B | 02 | 0F | 06 |

| RS      | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| R/Not W | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Note: Check Busy Flag (BF) before steps 1, 3, 5, 7, 9 and 11. All values are hexadecimal.

## 8.11 Read BUSY FLAG

| R/Not W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Function       |

|---------|----|-----|-----|-----|-----|-----|-----|-----|-----|----------------|

| 1       | 1  | BF  | *   | *   | *   | *   | *   | *   | *   | Read BUSY FLAG |

This instruction is used to check whether the HD61830(B) is in the BUSY state or not. The BUSY FLAG (BF) should be checked before initiating any instruction to the HD61830(B), except when data is written in the register (RS=1).

**BF**=1:HD61830(B) is BUSY **BF**=0:HD61830(B) is not BUSY

#### Table 8.12: Busy Signal Timing

| Function                 | BUSY             |                      |                                      |  |  |  |  |  |  |  |

|--------------------------|------------------|----------------------|--------------------------------------|--|--|--|--|--|--|--|

|                          | <b>BUSY FLAG</b> | Min.                 | Max.                                 |  |  |  |  |  |  |  |

| Write Instruction (RS=1) | NOT SET          | -                    | 1µs                                  |  |  |  |  |  |  |  |

| Write Data (RS=0)        | SET              | t <sub>CL2</sub>     | 2 x t <sub>CL2</sub>                 |  |  |  |  |  |  |  |

| Read/Write VRAM          | SET              | 2 x t <sub>CL2</sub> | $(2 + H_P)t_{CL2}$                   |  |  |  |  |  |  |  |

| BIT Set/Clear            | SET              | $(2 + H_P)t_{CL2}$   | 2(H <sub>P</sub> +1)t <sub>CL2</sub> |  |  |  |  |  |  |  |

**Note:** A safety factor of 3 times the maximum BUSY time indicated above should be used if the Busy Flag is not polled by the MPU before each instruction is sent to the HD61830(B).

# 9.0 Definitions for $H_P$ , $H_N$ , $V_P$ , $C_P$ , $N_X$

| Symbol         | Name                          | Meaning                                                                                                                           | Value                               |

|----------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| H <sub>P</sub> | Horizontal<br>character pitch | Horizontal character pitch                                                                                                        | 6 to 8 dots                         |

| H <sub>N</sub> |                               | Number of horizontal characters per line (number of digits) in the character mode or number of bytes per line in the graphic mode | 2 to 128 digits (an<br>even number) |

| V <sub>P</sub> | Vertical character<br>pitch   | Vertical character pitch                                                                                                          | 1 to 16 dots                        |

| C <sub>P</sub> | Cursor position               | Line number on which the cursor can be displayed                                                                                  | 1 to 16 lines                       |

| N <sub>X</sub> | Number of time<br>divisions   | Inverse of display duty ratio                                                                                                     | 1 to 128 lines                      |

Note: If the number of vertical dots on the screen is "m", and the number of dots is "n".

$1/m = 1/N_X =$  display duty ratio n = H<sub>P</sub> x H<sub>N</sub>, m/V<sub>P</sub> = Number of display lines C<sub>P</sub>  $\leq$  V<sub>P</sub>

# 10.0 Relationship between Display Mode, VRAM data and LCD dots.

| Display Mode      | Display Data From MPU   | RAM                                         | Liquid Crystal Display Panel |

|-------------------|-------------------------|---------------------------------------------|------------------------------|

|                   |                         |                                             | <-> H <sub>P</sub>           |

|                   |                         | Start address -><br>b7 b6 b5 b4 b3 b2 b1 b0 | АВС                          |

| Character Display | Character Code (8 bits) | 0 1 0 0 0 0 1<br>0 1 0 0 0 0 1 0            |                              |

| Assume: H <sub>P</sub> =6;<br>V <sub>P</sub> =8 | LCD<br>Format |    | 32 x<br>128 | 64 x<br>128 | 64 x<br>128<br>1/64 | 64 x<br>240<br>1/32 | 64 x<br>240<br>1/64 | 64 x<br>480 | 128 x<br>128 | 128 x<br>240 | 128 x<br>256 |

|-------------------------------------------------|---------------|----|-------------|-------------|---------------------|---------------------|---------------------|-------------|--------------|--------------|--------------|

| Register/                                       |               |    | 1/32        | 1/32        |                     |                     |                     | 1/64        | 1/128        | 1/128        | 1/64         |

| Data                                            | R/W           | RS |             |             |                     |                     |                     |             |              |              |              |

| Mode Control Reg                                | 0             | 1  | 00H         | 00H         | 00H                 | 00H                 | 00H                 | 00H         | 00H          | 00H          | 00H          |

| Mode Control data                               | 0             | 0  | 34H         | 34H         | 34H                 | 34H                 | 34H                 | 34H         | 34H          | 34H          | 34H          |

| Character Pitch<br>Reg                          | 0             | 1  | 01H         | 01H         | 01H                 | 01H                 | 01H                 | 01H         | 01H          | 01H          | 01H          |

| Vert/Horiz Pitch<br>data                        | 0             | 0  | 75H         | 75H         | 75H                 | 75H                 | 75H                 | 75H         | 75H          | 75H          | 75H          |

| Horiz. Count Reg                                | 0             | 1  | 02H         | 02H         | 02H                 | 02H                 | 02H                 | 02H         | 02H          | 02H          | 02H          |

| Horiz. Count data<br>(HN-1)                     | 0             | 0  | 13H         | 13H         | 13H                 | 27H                 | 27H                 | 4FH         | 13H          | 27H          | 29H          |

| Multiplex Ratio<br>Reg.                         | 0             | 1  | 03H         | 03H         | 03H                 | 03H                 | 03H                 | 03H         | 03H          | 03H          | 03H          |

| (1/Duty-1), (NX-1)                              | 0             | 0  | 1FH         | 1FH         | 3FH                 | 1FH                 | 3FH                 | 3FH         | 7FH          | 7FH          | 3FH          |

| Cursor Position<br>Reg                          | 0             | 1  | 04H         | 04H         | 04H                 | 04H                 | 04H                 | 04H         | 04H          | 04H          | 04H          |

| Cursor Position                                 | 0             | 0  | 07H         | 07H         | 07H                 | 07H                 | 07H                 | 07H         | 07H          | 07H          | 07H          |

| Start Addr (L) Reg                              | 0             | 1  | 08H         | 08H         | 08H                 | 08H                 | 08H                 | 08H         | 08H          | 08H          | 08H          |

| Display Start Addr<br>(L)                       | 0             | 0  | 00H         | 00H         | 00H                 | 00H                 | 00H                 | 00H         | 00Н          | 00H          | 00H          |

| Start Addr (H) Reg                              | 0             | 1  | 09H         | 09H         | 09H                 | 09H                 | 09H                 | 09H         | 09H          | 09H          | 09H          |

| Display Start Addr<br>(H)                       | 0             | 0  | 00H         | 00H         | 00H                 | 00H                 | 00H                 | 00H         | 00H          | 00H          | 00H          |

| Cursor Address<br>(L) Reg                       | 0             | 1  | 0AH         | 0AH         | 0AH                 | 0AH                 | 0AH                 | 0AH         | 0AH          | 0AH          | 0AH          |

| Cursor Address (L)                              | 0             | 0  | 00H         | 00H         | 00H                 | 00H                 | 00H                 | 00H         | 00H          | 00H          | 00H          |

| Cursor Address<br>(H) Reg                       | 0             | 1  | 0BH         | 0BH         | 0BH                 | 0BH                 | 0BH                 | 0BH         | овн          | овн          | 0BH          |

| Cursor Address (H)                              | 0             | 0  | 00H         | 00H         | 00H                 | 00H                 | 00H                 | 00H         | 00H          | 00H          | 00H          |

# 12.2 Graphics Mode Initialization:

| Assume: H <sub>P</sub> =8    | LCDFormat |    | 32 x<br>128 | 64 x<br>128 | 64 x<br>128<br>1/64 | 64 x<br>240<br>1/32 | 64 x<br>240<br>1/64 | 64 x<br>480 | 128 x<br>128 | 128 x<br>240 | 128 x<br>256 |

|------------------------------|-----------|----|-------------|-------------|---------------------|---------------------|---------------------|-------------|--------------|--------------|--------------|

| Register/                    |           |    | 1/32        | 1/32        |                     |                     |                     | 1/64        | 1/128        | 1/128        | 1/64         |

| Data                         | R/W       | RS |             |             |                     |                     |                     |             |              |              |              |

| Mode Control Reg             | 0         | 1  | 00H         | 00H         | 00H                 | 00H                 | 00H                 | 00H         | 00H          | 00H          | 00H          |

| Mode Control data            | 0         | 0  | 32H         | 32H         | 32H                 | 32H                 | 32H                 | 32H         | 32H          | 32H          | 32H          |

| Character Pitch<br>Reg       | 0         | 1  | 01H         | 01H         | 01H                 | 01H                 | 01H                 | 01H         | 01H          | 01H          | 01H          |

| Vert/Horiz Pitch<br>data     | 0         | 0  | 77H         | 77H         | 77H                 | 77H                 | 77H                 | 77H         | 77H          | 77H          | 77H          |

| Horiz. Count Reg             | 0         | 1  | 02H         | 02H         | 02H                 | 02H                 | 02H                 | 02H         | 02H          | 02H          | 02H          |

| Horiz. Count data,<br>(HN-1) | 0         | 0  | 0FH         | 0FH         | 0FH                 | 1DH                 | 1DH                 | 3BH         | 0FH          | 1DH          | 1FH          |

| Multiplex Ratio<br>Reg.      | 0         | 1  | 03H         | 03H         | 03H                 | 03H                 | 03H                 | 03H         | 03H          | 03H          | 03H          |

| (1/Duty-1), (NX-1)           | 0         | 0  | 1FH         | 1FH         | 3FH                 | 1FH                 | 3FH                 | 3FH         | 7FH          | 7FH          | 3FH          |

| Cursor Position<br>Reg       | 0         | 1  | 04H         | 04H         | 04H                 | 04H                 | 04H                 | 04H         | 04H          | 04H          | 04H          |

| Cursor Position              | 0         | 0  | 07H         | 07H         | 07H                 | 07H                 | 07H                 | 07H         | 07H          | 07H          | 07H          |

|                           | - |   |     |     |     |     |     |     |     |     |     |

|---------------------------|---|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Start Addr (L) Reg        | 0 | 1 | 08H |

| Display Start Addr<br>(L) | 0 | 0 | 00H |

| Start Addr (H) Reg        | 0 | 1 | 09H |

| Display Start Addr<br>(H) | 0 | 0 | 00H |

| Cursor Address<br>(L) Reg | 0 | 1 | 0AH |

| Cursor Address (L)        | 0 | 0 | 00H |

| Cursor Address<br>(H) Reg | 0 | 1 | 0BH |

| Cursor Address (H)        | 0 | 0 | 00H |

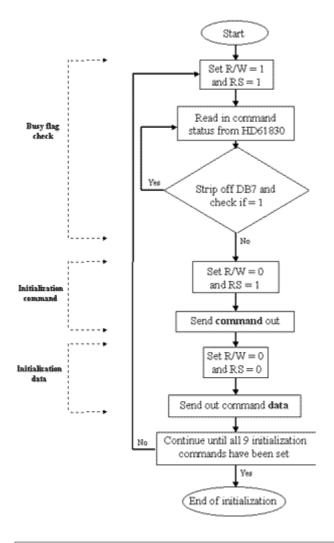

# 12.3 Initialization Flow Diagram

# 13.0 Trouble shooting Guide

| Symptoms                                                                       | Possible Solutions                        |

|--------------------------------------------------------------------------------|-------------------------------------------|

| Display appears blank                                                          | 1, 2, 3, 5, 6, 7, 8, 9, 10, 12, 13,<br>14 |

| Displayed characters entered unreliably or at random                           | 2, 3, 4                                   |

| Descender characters such as " g, j, y, p, q " etc are broken or do not appear | 17, 11                                    |

| Missing column segments or pixels                                              | 13                                        |

| Excessive heat generated by LSI chips or excessive I <sub>DD</sub> current     | 1, 14                                     |

| Unable to read VRAM or Busy flag                                               | 1, 3, 7, 9, 10                            |

| EL Backlight will not function or is too dim                                   | 15                                        |

| LED backlight will not function or is too bright or runs too hot               | 16                                        |

#### Possible Solutions:

- 1. Check voltage level and polarity of  $V_{DD}$  and  $V_{SS}$  at display connector. The  $V_{DD}$  logic supply voltage should be in the range 4.75VDC <  $V_{DD}$  < 5.25VDC with respect to  $V_{SS}$ (GND). Also check that  $V_{DD}$  and  $V_{SS}$  noise, is within limits.

- 2. Check the pulse width of (Not RST) is within specified limits or the HD61830(B) will not be reset properly and internal registers will not be initialized. Also check when testing numerous displays on the same test set-up that the VDD voltage is turned off before connecting or disconnecting LCD modules. Note that on power-up the contents of the VRAM are not cleared and will contain random data. It is best to set every location of VRAM to a known state as part of any initialization procedure.

- 3. Check that the positive going enable pulse "E" is at least 450ns wide and that all Hold and Set-up timing requirements are met as shown in section 5.1.

- 4. Ensure that data is not being transmitted too fast to the HD61830. Always pole the BUSY flag before sending instructions (section 8.11). If MPU is not reading the BUSY flag before writing instructions, allow an adequate delay between instructions.

- 5. Check the voltage level at the V<sub>o</sub> pin is at the correct voltage for the ambient temperature conditions as specified by individual LCD module data sheets.

- 6. Check the continuity of the cable between the host MPU and the LCD module. Check for broken connections, loose crimps or dry joints on soldered connections. Minimize the length of this cable to reduce cross-talk and noise pick-up. (about 50cm)

- 7. Check that the data bus of the HD61830 (DB0-DB7) is not excessively loaded during read operations.

- 8. Check the voltage levels of input signals is as specified by the LCD module data sheet.

- 9. Check that no more than one external bus device is selected during read operations so as to cause bus contention and erroneous data transfer.

- 10. Check for damage to PCB traces and plated through Via holes.

- 11. Check that LCD module has been initialized for correct DUTY cycle. and V<sub>P</sub> and H<sub>P</sub> are correctly set for 5x11 font (section 8.2).

- 12. Check that Display ON/OFF flag is set otherwise display will appear blank.

- 13. Check that LCD module has not been mishandled by applying excessive shock of mechanical stress which will cause the LC glass to misalign with the Elastomer strips that connect the LC glass to the PCB.

- 14. Check that LCD module has not been mishandled by applying excessive electrical stress in the form of electro-static discharge (ESD) or by applying reverse voltage to V<sub>DD</sub> and V<sub>SS</sub>. Always use electro-static handling precautions, grounded wrist straps and bench mats when handling LCD modules as they use CMOS LSI chips. Always use a grounded soldering iron when mounting connectors to the LCD module.

- 15. Check connections between EL backlight, DC-AC inverter, and the EL lamp mounted on the LCD module. Check input voltage to DC-AC inverter. Never operate the DC-AC inverter without an EL Lamp load, as this may damage the inverter. EL backlights dim with age and need to be replaced when their brightness level is no longer adequate.

- 16. Check that the correct series current limiting resistor for the LED backlight is in place between the power supply and the LED lamp. Check individual LCD module data sheets for maximum forward current, I<sub>f</sub>, for LED backlight. The LED's may burn-out if the maximum forward current, I<sub>f</sub>, is

exceeded. Some, but not all, LED backlight modules will already have the current limiting resistor

on-board.

17. This problem is symptomatic of trying to use the 5x11 font selection when  $V_p$ <12 (section 8.2). Reprogram the Character Pitch Register so that  $V_p$ =12.

## 14.0 Internal Character Generator Font Pattern and Character Codes

| V <u>msb_lsb</u> > | 0     | 1   | 2   | 3        | 4   | 5   | 6   | 7   | 8   | 9   | Α   | В   | С   | D   | Ε             | F            |

|--------------------|-------|-----|-----|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---------------|--------------|

| 2                  | blank | !   | "   | #        | \$  | %   | &   | "   | (   | )   | *   | +   | ,   | -   | •             | /            |

| 3                  | 0     | 1   | 2   | 3        | 4   | 5   | 6   | 7   | 8   | 9   | :   | ;   | <   | =   | >             | ?            |

| 4                  | @     | А   | В   | С        | D   | E   | F   | G   | Н   | I   | J   | K   | L   | М   | Ν             | 0            |

| 5                  | Ρ     | Q   | R   | S        | Т   | U   | V   | W   | Х   | Y   | Ζ   | [   | ¥   | ]   | ^             |              |

| 6                  | ١     | а   | b   | С        | d   | е   | f   | g   | h   | i   | j   | k   | I   | m   | n             | 0            |

| 7                  | р     | q   | r   | s        | t   | u   | v   | w   | Х   | у   | z   | {   |     | }   | $\rightarrow$ | $\leftarrow$ |

| Α                  | ***   | *** | *** | ***      | *** | *** | *** | *** | *** | *** | *** | *** | *** | *** | ***           | ***          |

| В                  | ***   | *** | *** | ***      | *** | *** | *** | *** | *** | *** | *** | *** | *** | *** | ***           | ***          |

| C                  | ***   | *** | *** | ***      | *** | *** | *** | *** | *** | *** | *** | *** | *** | *** | ***           | ***          |

| D                  | ***   | *** | *** | ***      | *** | *** | *** | *** | *** | *** | *** | *** | *** | *** | ***           | ***          |

| E                  | α     | ä   | ß   | ε        | μ   | σ   | р   | g   |     | -1  | j   | х   | ¢   | £   | ñ             | ö            |

| F                  | р     | q   | Ø   | $\infty$ | Ω   | ü   | Σ   | П   | х   | у   |     |     |     | ÷   | blank         | 1            |

\*\*\*Characters defined from A0 to DF is part of the Kanji character set. For a description of these characters please contact Hitachi or your local Densitron Corporation.

**Note:** Character defined from E0 to FF are part of a 5x11 font structure and will only work properly on an alphanumeric with the same LCD structure.

# Amendment 001 to document AN-01

regarding mapping of VRAM in the LM3165 and LM4165

When programming the LM3165 or LM4165, special consideration must be given in the mapping of the VRAM to the LCD dots. Due to the nature of the HD61830, portions of the VRAM might not be visible on the display. The HD61830 can map up to a 128 x 240 dot format. Since the LM3165 and 4165 have a resolution of 128 x 128, the mapping is so that the first 112 memory allocations are off the left hand side of the LCD display. So when writing in the VRAM, both graphics and text, make sure you include this offset of 112 (or 19 for text).

There is another unique feature to the 128 x 128 that pertains to the mapping of the VRAM in character mode only. Not only is the offset still necessary, but the portion of memory usually left available for text is split in two. The first of these two portions is responsible for the odd rows of the display, and the second for the even rows. For example, to place the letter "A" (5x7) in the upper left hand corner of the display, you must place a 41H in memory location 0013H and in memory location 1013H.

This at first may appear that this mapping will double your code length, but this can be done simply in your subroutine responsible for clocking in data. After your text has been clocked into the specific memory allocation, add 1000H to this memory address and re-clock in the data again. Subtracting 1000H after this operation will put your counter back on track. This upper location of memory must also be cleared out when starting your text to eliminate garbage that is present in memory from boot up. The total portions of VRAM that should be cleared in text mode are locations 13H to 280H and 1013H to 1280H.